# 400Gb/s QSFP-DD DR4 Optical Transceiver Moudule

#### **General Description**

Gearlink's 400-Gbps QSFP-DD DR4 Optical Transceiver Module with Quad Small Form-Factor Pluggable

Double Density (QSFP-DD) form-factor is of high performance in bi-directional signal transmission and aggregate 400Gbps bandwidth, which design to follow QSFP DD MSA and 400GBASE-DR4 of IEEE 802.3bs standard and ultra-low power consumption of 8 W for 400G QSFP-DD D`R4+ are also proven..

Compared with the conventional copper-based direct attach cables (DACs), the optical fiber with pluggable MPO connector enables the ease of complicated data center cabling deployment by the longer, lighter, and bendable characteristics. The optical transceiver module utilizes high-performance 1310-nm EML and PIN PDs with superior integration in signal integrity and optical sub-assembly, whose bit-error-rate is better than 2.4 E-4 for reliable packet communication within data center.

#### **Features**

- Compliance to 400GBASE-DR4 of IEEE 802.3 bs Rev. 3.5

- Compliance to QSFP DD MSA Rev 4.0 (for Memory Map)

and 5.0 (for Mechanical QSFP-DD Housing)

- Per CMIS 4, support functions of Module Diagnostics and Remote Firmware Upgrade

- Supports 400 Gbps data rate links up to 500m via SMF.

- Maximum Power Consumption: 8W

- Hot pluggable electrical interface Using standard 12

Channel MPO/APC Connector

- 0 to 70°C case temperature operating range

- RoHS-6 Compliant (lead-free)

## **Application**

- Ethernet for 400GBASE-DR4

- For 400 Gb/s Ethernet Application

- HPC Interconnects

- Proprietary Interconnections

Not necessarily applied together. Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

# **Absolute Maximum Rating**

Not necessarily applied together. Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

| Parameter                          | Min  | Max | Unit    | Note |

|------------------------------------|------|-----|---------|------|

| Storage Temperature                | -40  | 85  | oC      |      |

| 3.3V Power Supply Voltage          | -0.5 | 3.6 | V       |      |

| Data Input Voltage- Single Ended   | -0.5 |     | Vcc+0.5 |      |

| Control Input Voltage              | -0.5 | 3.6 | V       |      |

| Relative Humidity                  | 5    | 85  | %       |      |

| Rx Optical Damage Threshold / Lane | 5    |     | dBm     |      |

Notes: 1. Non-condensing.

## **Recommended Operating Conditions**

| Parameter                             | Min   | Typical | Max                  | Unit | Note    |

|---------------------------------------|-------|---------|----------------------|------|---------|

| Case Operating Temperature            | 0     |         | 70                   | °C   |         |

| Power Supply Voltage                  | 3.135 | 3.3     | 3.465                | V    |         |

| Date Rate per Channel                 |       |         | 53.125               | Gbps |         |

| Bit Error Ratio (BER)                 |       |         | 2.4x10 <sup>-4</sup> |      | 1, 2    |

| Control Input Voltage High            | 2     |         | Vcc+0.3              | V    |         |

| Control Input Voltage Low             | -0.3  |         | 0.8                  | V    |         |

| Two Wire Serial (TWS) Interface Clock |       |         | 1                    | MHz  |         |

| Differential Data Input / Output Load |       | 100     |                      | Ohms | +/- 10% |

| Link Distance                         |       |         | 500                  | m    |         |

#### Notes:

#### **Electrical Characteristics**

| Parameter                                               | Symbol            | Min  | Typical | Max | Unit | Note |  |  |

|---------------------------------------------------------|-------------------|------|---------|-----|------|------|--|--|

| Transceiver Electrical Characteristics                  |                   |      |         |     |      |      |  |  |

| TRx Power Consumption                                   |                   |      | 8       | 10  | W    |      |  |  |

| 400GAUI-8 Module Electrical Input Characteristics (TP1) |                   |      |         |     |      |      |  |  |

| Date Rate per Channel                                   |                   |      | 26.5625 |     | GBd  |      |  |  |

| Single Ended Input Voltage Tolerance                    |                   | -0.4 |         | 3.3 | V    |      |  |  |

| Differential pk-pk input voltage                        |                   |      |         | 880 | mV   |      |  |  |

| Differential Input Return Loss                          | Sdd <sub>11</sub> |      |         |     | dB   | 1    |  |  |

| Common to differential modeconversion return loss       | $Scd_{11}$        |      |         | dB  | 2    |      |  |  |

| DC common mode voltage                                  |                   | -0.3 |         | 2.8 | V    |      |  |  |

<sup>1.</sup> Bit-Error-Rate (BER) is tested with PRBS 31Q pattern.

$<sup>2.\,\,400</sup>G\,\,QSFP\text{-}DD\,\,DR4\,\,requires\,\,an\,\,electrical\,\,connector\,\,compliant\,\,with\,\,QSFP\text{-}DD\,\,MSA\,\,which\,\,is\,\,used\,\,on\,\,the\,\,host\,\,board\,\,in\,\,order\,\,to\,\,guarantee\,\,its\,\,electrical\,\,interface\,\,specification.$

| AC Common-Mode Output Voltage (RMS)                |                   |       |  | 17.5 | mV |   |

|----------------------------------------------------|-------------------|-------|--|------|----|---|

| Differential Output Voltage                        |                   |       |  | 900  | mV |   |

| Near-end ESMW (Eye symmetry mask width)            |                   | 0.265 |  |      | UI |   |

| Far-end ESMW (Eye symmetry mask width)             |                   | 0.2   |  |      | UI |   |

| Near-end Eye Height                                |                   | 70    |  |      | mV |   |

| Far-end Eye Height                                 |                   | 30    |  |      | mV |   |

| Differential Output Return Loss                    | Sdd <sub>22</sub> |       |  | dB   | 1  |   |

| Common to Differential Mode Conversion Return Loss | Scd <sub>22</sub> |       |  |      | dB | 2 |

| Transition Time (20% to 80%)                       |                   | 9.5   |  |      | ps |   |

| DC Common Voltage                                  |                   | -350  |  | 2850 | mV |   |

# **Optical Characteristics**

| Parameter                                                 | Symbol | Min    | Typical | Max    | Unit | Note |  |  |  |

|-----------------------------------------------------------|--------|--------|---------|--------|------|------|--|--|--|

| Transmitter Optical Characteristics                       |        |        |         |        |      |      |  |  |  |

| Center Wavelength                                         | λ      | 1304.5 |         | 1317.5 | nm   |      |  |  |  |

| Side-Mode Suppression Ratio                               | SMSR   | 30     |         |        | dB   |      |  |  |  |

| Average launch power, each lane                           | LOP    | -2.9   |         | 4      | dBm  |      |  |  |  |

| Output Optical Modulation Amplitude, per Lane             | OMA    | -0.8   |         | 4.2    | dBm  |      |  |  |  |

| Transmitter and dispersion eye closure (TDECQ), each lane | TDECQ  |        |         | 3.4    | dB   |      |  |  |  |

| Extinction ratio                                          | ER     | 3.5    |         |        | dB   |      |  |  |  |

| Center Wavelength                                         | λ      | 1304.5 |         | 1317.5 | nm   |      |  |  |  |

| Damage Threshold                                          |        | 5      |         |        | dBm  |      |  |  |  |

| Average receive power, each lane                          |        | -5.9   |         | 4      | dBm  | 1    |  |  |  |

| Receive power (OMA <sub>outer</sub> ), each lane          |        |        |         | 4.2    | dBm  |      |  |  |  |

| Receiver Reflectance                                      |        |        |         | -26    | dB   |      |  |  |  |

| Receiver sensitivity (OMA <sub>outer</sub> )              |        |        |         | -4.4   | dBm  | 2    |  |  |  |

| Stressed receiver sensitivity                             |        |        |         | -1.9   | dBm  | 3    |  |  |  |

| Conditions of stressed receiver sensitivity test:         |        |        |         |        |      |      |  |  |  |

| Stressed eye closure for PAM4 (SECQ), lane                |        |        | 3.4     |        | dB   |      |  |  |  |

| OMA <sub>outer</sub> of each aggressor lane               |        |        | 4.2     |        | dBm  |      |  |  |  |

# Notes:

- 1. each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 2. Receiver sensitivity (OMAouter), each lane (max) is informative and is defined for a transmitter with SECQ of 0.9 dB.

- 3. Measured with conformance test signal at TP3 for the BER of 2.4x10-4

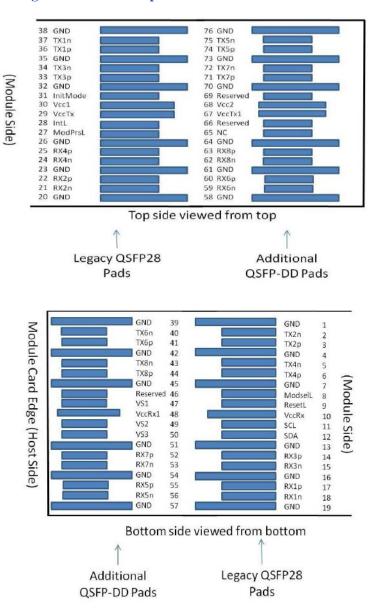

Module Card Edge (Host Side)

## **QSFP-DD** Module Pad Assignments and Descriptions

| Pin | Logic      | Symbol   | Description                                           | Plug Sequence | Notes |

|-----|------------|----------|-------------------------------------------------------|---------------|-------|

| 1   |            | GND      | Ground                                                | 1B            | 1     |

| 2   | CML-I      | Tx2n     | Transmitter Inverted Data Input                       | 3B            |       |

| 3   | CML-I      | Tx2p     | Transmitter Non-Inverted Data Input                   | 3B            |       |

| 4   |            | GND      | Ground                                                | 1B            | 1     |

| 5   | CML-I      | Tx4n     | Transmitter Inverted Data Input                       | 3B            |       |

| 6   | CML-I      | Tx4p     | Transmitter Non-Inverted Data Input                   | 3B            |       |

| 7   |            | GND      | Ground                                                | 1B            | 1     |

| 8   | LVTTL-I    | ModSelL  | Module Select                                         | 3B            |       |

| 9   | LVTTL-I    | ResetL   | Module Reset                                          | 3B            |       |

| 10  |            | VccRx    | +3.3V Power Supply Receiver                           | 2B            | 2     |

| 11  | LVCMOS-I/O | SCL      | 2-wire serial interface clock                         | 3B            |       |

| 12  | LVCMOS-I/O | SDA      | 2-wire serial interface data                          | 3B            |       |

| 13  |            | GND      | Ground                                                | 1B            | 1     |

| 14  | CML-O      | Rx3p     | Receiver Non-Inverted Data Output                     | 3B            |       |

| 15  | CML-O      | Rx3n     | Receiver Inverted Data Output                         | 3B            | 1     |

| 16  |            | GND      | Ground                                                | 1B            |       |

| 17  | CML-O      | Rx1p     | Receiver Non-Inverted Data Output                     | 3B            |       |

| 18  | CML-O      | Rx1n     | Receiver Inverted Data Output                         | 3B            |       |

| 19  |            | GND      | Ground                                                | 1B            | 1     |

| 20  |            | GND      | Ground                                                | 1B            | 1     |

| 21  | CML-O      | Rx2n     | Receiver Inverted Data Output                         | 3B            |       |

| 22  | CML-O      | Rx2p     | Receiver Non-Inverted Data Output                     | 3B            |       |

| 23  |            | GND      | Ground                                                | 1B            | 1     |

| 24  | CML-O      | Rx4n     | Receiver Inverted Data Output                         | 3B            |       |

| 25  | CML-O      | Rx4p     | Receiver Non-Inverted Data Output                     | 3B            |       |

| 26  |            | GND      | Ground                                                | 1B            | 1     |

| 27  | LVTTL-O    | ModPrsL  | Module Present                                        | 3B            |       |

| 28  | LVTTL-O    | IntL     | Interrupt                                             | 3B            |       |

| 29  |            | VccTx    | +3.3V Power supply transmitter                        | 2B            | 2     |

| 30  |            | Vcc1     | +3.3V Power supply                                    | 2B            | 2     |

| 31  | LVTTL-I    | InitMode | Initialization mode; In legacy QSFP applications, the | 3B            |       |

| 32  |            | GND      | Ground                                                | 1B            | 1     |

| 33  | CML-I      | Tx3p     | Transmitter Non-Inverted Data Input                   | 3B            |       |

| 34  | CML-I      | Tx3n     | Transmitter Inverted Data Input                       | 3B            |       |

| 35  |            | GND      | Ground                                                | 1B            | 1     |

| 36  | CML-I      | Tx1p     | Transmitter Non-Inverted Data Input                   | 3B            |       |

| 37  | CML-I      | Tx1n     | Transmitter Inverted Data Input                       | 3B            |       |

| 38  |            | GND      | Ground                                                | 1B            | 1     |

| 39  |            | GND      | Ground                                                | 1A            | 1     |

| 40  | CML-I      | Tx6n     | Transmitter Inverted Data Input                       | 3A            |       |

| 41   | CML-I | Тх6р     | Transmitter Non-Inverted Data Input | 3A |   |

|------|-------|----------|-------------------------------------|----|---|

| 42   |       | GND      | Ground                              | 1A | 1 |

| 43   | CML-I | Tx8n     | Transmitter Inverted Data Input     | 3A |   |

| 44   | CML-I | Tx8p     | Transmitter Non-Inverted Data Input | 3A |   |

| 45   |       | GND      | Ground                              | 1A | 1 |

| 46   |       | Reserved | For future use                      | 3A | 3 |

| 47   |       | VS1      | Module Vendor Specific 1            | 3A | 3 |

| 48   |       | VccRx1   | 3.3V Power Supply                   | 2A | 2 |

| 49   |       | VS2      | Module Vendor Specific 2            | 3A | 3 |

| 50   |       | VS3      | Module Vendor Specific 3            | 3A | 3 |

| 51   |       | GND      | Ground                              | 1A | 1 |

| 52   | CML-O | Rx7p     | Receiver Non-Inverted Data Output   | 3A |   |

| 53   | CML-O | Rx7n     | Receiver Inverted Data Output       | 3A |   |

| 54   |       | GND      | Ground                              | 1A | 1 |

| 55   | CML-O | Rx5p     | Receiver Non-Inverted Data Output   | 3A |   |

| 56   | CML-O | Rx5n     | Receiver Inverted Data Output       | 3A |   |

| 57   |       | GND      | Ground                              | 1A | 1 |

| 58   |       | GND      | Ground                              | 1A | 1 |

| 59   | CML-O | Rx6n     | Receiver Inverted Data Output       | 3A |   |

| 60   | CML-O | Rx6p     | Receiver Non-Inverted Data Output   | 3A |   |

| 61   |       | GND      | Ground                              | 1A | 1 |

| 62   | CML-O | Rx8n     | Receiver Inverted Data Output       | 3A |   |

| 63   | CML-O | Rx8p     | Receiver Non-Inverted Data Output   | 3A |   |

| 64   |       | GND      | Ground                              | 1A | 1 |

| 65   |       | NC       | No Connect                          | 3A | 3 |

| 66   |       | Reserved | For future use                      | 3A | 3 |

| 67   |       | VccTx1   | 3.3V Power Supply                   | 2A | 2 |

| 68   |       | Vcc2     | 3.3V Power Supply                   | 2A | 2 |

| 69   |       | Reserved | For Future Use                      | 3A | 3 |

| 70   |       | GND      | Ground                              | 1A | 1 |

| 71   | CML-I | Tx7p     | Transmitter Non-Inverted Data Input | 3A |   |

| 72   | CML-I | Tx7n     | Transmitter Inverted Data Input     | 3A |   |

| 73   |       | GND      | Ground                              | 1A | 1 |

| 74   | CML-I | Tx5p     | Transmitter Non-Inverted Data Input | 3A |   |

| 75   | CML-I | Tx5n     | Transmitter Inverted Data Input     | 3A |   |

| 76   |       | GND      | Ground                              | 1A | 1 |

| Note |       |          |                                     |    |   |

Note

<sup>1.</sup> QSFP-DD uses common ground (GND)for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

<sup>2.</sup> Note 2: VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 6. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins are each rated for a maximum current of 1000 mA.

<sup>3.</sup> All Vendor Specific, Reserved and No Connect pins may be terminated with 50 ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF.

4. Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A, 1B will then occur simultaneously, followed by 2A, 2B, followed by 3A,3B.

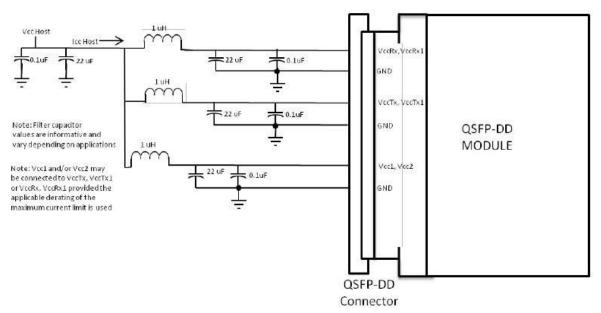

## **Recommended Host Board Power Supply Circuit**

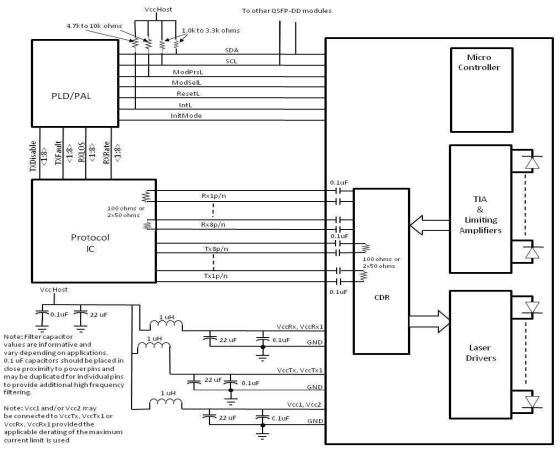

#### **Recommended Interface Circuit**

QSFP-DD Optical Module

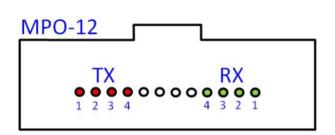

Optical-Channel Definition for 1 Row x 12C Fiber

#### **Memory Map**

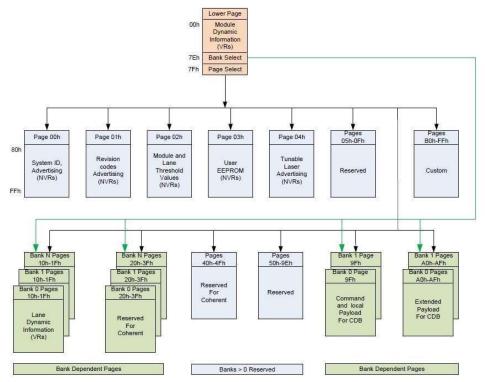

The memory map is structured as a single address and multiple page approaches, according to the QSFP-DD rev.4.0 specification as shown in the below. For more detailed description of this memory map, please see our Memory Map document with flexible customization settings. Current FW can support page  $00h \sim 03h$  and Page  $10h \sim 11h$  and will implement the rest in the near future.

**Regulatory Compliance Table**

| Item                                       | Compliance                                                                 |   |  |  |

|--------------------------------------------|----------------------------------------------------------------------------|---|--|--|

| Electrostatic Discharge (ESD) to the       | JEDEC Human Body Model (HBM) (JESD22-A114-B)                               | 1 |  |  |

| Electrostatic Discharge (ESD) EN 61000-4-2 |                                                                            | 1 |  |  |

| Electromagnetic Interference (EMI)         | 47 CFR FCC Rules and Regulations Part 15 Subpart B, Class B Digital Device |   |  |  |

|                                            | EN 55032:2015/AC:2016, Class B                                             | 1 |  |  |

| Immunity EN 55024:2010/A1:2015             |                                                                            | 1 |  |  |

| Laser Safety                               | EN 60825-1:2007 and IEC 60825-1:2014                                       | 1 |  |  |

The 400G QSFP-DD DR4 samples are on-going to be prepared for these testing items.